# ON-CHIP FFT SPECTRAL ANALYSIS OF MULTI TONE SIGNALS WITH LOW COMPLEXITY FOR BUILT-IN TESTING AND CALIBRATION APPROACH

**S.SARANYA<sup>1</sup>**, **S.SELVARASI<sup>2</sup>**<sup>1</sup>PG student, VLSI Design, <sup>2</sup>Assistant professor, <sup>1,2</sup>Dept of Information and communication Engineering, <sup>1,2</sup>Surya group of institutions, vikravandi, India

#### Abstract

The Fast Fourier Transform (FFT) algorithm is a standard tool to carry out spectral analysis. However, the presence of multi tone signal requires large number of FFT points results large area and power overheads. In this paper, FFT method is proposed for on-chip spectral analysis of multi tone signals with particular harmonics and inters modulation components. This FFT analysis approach is based on coherent sampling. The proposed on-chip testing scheme use Fast Fourier Transform (FFT) algorithm with fixed size and the smaller number of points to make the FFT realization is more suitable that requires area and power efficiency. The technique was assessed by comparing the simulation results for fixed point and variable point FFT. The results indicate that the proper selection of test tone frequencies can avoid spectral leakage even with multiple narrowly spaced tones.

### I. INTRODUCTION

Accurate frequency estimation of distorted and noisy signals in industrial power systems is a challenging problem that has attracted much attention. In power systems, the typical application of frequency estimation is for protection against loss of synchronism, under-frequency relaying, powerquality monitoring, and power system stabilization. De-noising and frequency recognition are of critical importance in practical deployment of signal communications. Many de-noising techniques exist in the literature. However, few of them are based on a general and rigorous framework, while at the same time demonstrating effectiveness in large-scale robust multi tone frequency recognition experiments. A key point of this work is to use of a strong on chip testing recognition model. The proposed built in self testing algorithm incorporates prior knowledge about the structure of signals, noise model, which is essential to its performance. A new method for frequency estimation technique is proposed using on chip built in self testing. In any case, the accuracy of the frequency estimation provided by the FFT is affected by errors due to the wideband noise superimposed onto the acquired data in the practical applications. There is a necessity to investigate the statistical behavior of the frequency estimation of distorted and noisy harmonic signals provided by simple and accurate interpolation algorithm. The reasons are given here. 1) The influence of a stationary white noise on the frequency estimation provided by the multipoint interpolation FFT based on the maximum side lobe decay window has been analyzed. The frequency estimations are based on the FFT which

uses the direct ratio of two maximum amplitude spectral lines and thus contains even items. However, there is a lack of the expression of the statistical behavior of the frequency estimation by the non-even item interpolation algorithm, which can avoid the even items in the spectral-peaks polynomial fitting procedures and provide fast and very high accuracy frequency estimation. 2) It is well known that spectral leakage suppression is obtained at the cost of widening the main lobe, and this increases noise contributions. In scientific literature, the accuracy of frequency estimation has been derived only for the FFT with the cosine windows. Since the selfconvolution windows own good sidelobe behaviors, it is important to know the influence of selfconvolution windows on the accuracy of frequency estimation.Digitally assisted analog design and integrated transceiver calibration approaches are gaining popularity in ensuring efficient and reliable mixed-signal systems in nano scale CMOS technologies. One design aspect is to equip analog blocks with performance-tuning features that allow the recovery from process variations and faults. Examples of such tuning mechanisms include input impedance matching, gain and center frequency tuning for low-noise amplifiers, second-order nonlinearity and mismatch correction for mixers, as well as linearity enhancements for baseband filters. The other aspect related to digitally assisted design is the extraction of performance metrics on the chip to enable one-time or periodic calibrations. Many performance characteristics can be observed based on the output spectrum of a circuit under test (CUT) or a

chain of analog blocks, which has led to on-chip spectrum analyzers that emulate conventional offchip instrumentation. Alternatively, calibration methods have been proposed that incorporate existing or dedicated analog-to-digital converter (ADC) and digital signal processing resources to directly quantize the output signals of analog circuits for the computation of the fast Fourier transform (FFT) and automatic tuning with digital-to-analog converters (DACs). Extraction of circuit linearity parameters with the latter approach calls for efficient FFT implementations, which is the focus of this paper. The presented method leverages that the frequencies for two-tone tests can be selected by the designer of the built-in test (BIT) or built-in calibration (BIC) scheme to circumvent inaccuracies due to spectral leakage while using a small number of FFT points. This capability to accurately measure the power of the tones as well as their distortion and inter modulation products with an efficient on-chip FFT can also find application in loopback testing techniques with spectral estimation.

# .II. RELATED WORK

The on-chip spectrum analyze ruses a digital frequency synthesizer [1] and a simple signal generator synchronized with a switched capacitor band pass filter. It consists of a digital frequency synthesizer, a switched-capacitor (SC) sine wave generator, a SC Band pass filter, a variable gain amplifier (VGA) and a final stage for the amplitude detection and/or digitization of the VGA output. pipelined FFT architecture, called mixed-radix multipath delay feedback (MRMDF), can provide a higher throughput rate by using the multi data-path scheme[2]. Furthermore, the hardware costs of memory and complex multipliers in MRMDF are only 38.9% and 44.8% of those in the known FFT processor by means of the delay feedback and the data scheduling approaches. The high-radix FFT algorithm is also realized in our processor to reduce the number of complex multiplications The cosineclass windows are some of the most used windows in analog to digital converter (ADC) dynamic testing [3] by spectral analysis when the coherent sampling condition cannot be fulfilled. A new indexed-scaling method is proposed to reduce both the critical-path delay[4] and hardware cost by employing shorter word length. Together with the mixed-radix multipath delay feedback structure, the proposed FFT processor can achieve very high throughput with low hardware cost. We explore the reuse of built-in digital calibration circuitry, along with minor digital design-for-testability (DfT)[5] modifications, to test and characterize analog/RF circuit performance. By

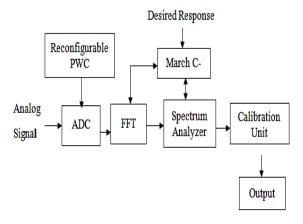

Fig 1. On-chip BIC approach with spectral testing

observing the digital tuning signals captured in the calibration circuitry. the performance can be closely estimated, thus enabling cost-effective Go/No-Go production testing. The realization of an on-chip block for built-in testing of RF transceivers[6] with the loopback method. The circuit is intended for cost-efficient production testing of RF front-end blocks with on-chip power detectors. A traditional loopback scheme is reconfigured with an analog filter and an adder implemented on a Device Interface Board (DIB), and a multiple tone input is applied to the DUTs .The spectral predictors are obtained from the Fourier representation of the loopback response [7] by measuring the magnitude of its fundamentals and harmonics.

#### III. PROPOSED APPROACH

Generally FFT is used for time to frequency transform at receiver end in wireless communication (e.g. 3G & 4G). Since all processing units are designed inside chip, there is possibility get distortion in spectrum due to single tone frequency or multi tone frequency or due to chip malfunctions. To get accurate spectrum or signal, we have to find out error or losses in spectrum. A built in spectrum analysis and calibration approach is proposed. This design analyzes spectrum samples of FFT output to determine distortions. Then Calibration tunes spectrum into required level. However this paper proposed FFT for 16 points that cannot be applicable

for 4<sup>th</sup> generation technologies. Also it has fixed sampling rate method failed to maintain tradeoff between speed and resolution. Here we propose a reconfigurable architecture that supports multiple inputs FFT for future communication technologies with tradeoff between speed and accuracy using reconfigurable pulse width modulation.

Fig 3.1 Block Diagram

#### a) ADC

It is a device that converts continuous physical quantity to digital number. Conversion involves Quantization of input, so it introduces small amount of error. Instead of doing a single conversion, ADC performs conversion ('Samples' the input) periodically. ADC is defined by its Bandwidth (the range of frequency it can measure) and it's SNR (how accurately it can measure a signal relative to the noise it introduces).

## b) Sample and Hold

It is to sample an analog input signal and hold this value over a certain length of time until the ADC can process the information. A/D Conversion involves a two step process:

- Quantizing is breaking down the analog value into a set of finite states.

- 2. Coding is assigning digital word or number to each state

#### c) SAR Architecture

Successive approximation employs a binary search algorithm in a feedback loop including a 1 bit A/D converter. The Following Figure 3.3: illustrates architecture which consists of a front end track & hold circuit, comparator, DAC and SAR logic. SAR logic is basically a shift register combined with decision logic and decision register. The pointer points to the last bit changed in the decision register

and the data stored in this register is the result of all comparisons performed during conversion period

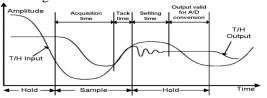

#### d) Track & Hold

A sample-and-hold (S/H) or track-and-hold (T/H) circuit is frequently required to capture rapidly varying signals for subsequent processing by slower circuitry. The function of the S/H circuit is to track/sample the analog input signal and to hold that value while subsequent circuitry digitizes it. The function of a track-and-hold circuit is to buffer its input signal accurately during track mode providing at its output a signal which is linearly proportional to the input, and to maintain a constant output level during hold mode equal to the T/H output value at the instant it was strobe from track to hold by an external clock signal.

Figure 3.2 waveforms of a practical sample-and-hold circuit.

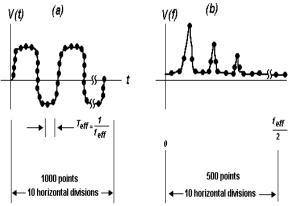

#### I. FAST FOURIER TRANSFORM

#### a) Testing with the Fast Fourier Transform

The simplest frequency-domain tests use the direct application of the fast Fourier transform. Taking the FFT of the output data while driving the A/D converter with a single, low distortion sine wave, the SNDR, ENOB, SFDR, and THD can easily be calculated. It is useful to take these measurements at several input amplitudes and frequencies, and plot the results. Taking data for high input frequencies allows the full-power and full-linear bandwidths to be calculated.Two more tests are completed while driving the A/D converter with an input composed of two sine waves of different frequencies. The FFT of this test result is used to calculate the IMD (for second-order and third-order products) and the twotone SFDR. The discrete (or digitized) version of the Fourier transform is called the Discrete Fourier Transform (DFT). This transform takes digitized time domain data and computes the frequency domain representation. While normal Fourier theory is useful for understanding how the time and frequency domain relate, the DFT allows us to compute the frequency domain representation of real-world time domain signals. This brings the power of Fourier theory out of the world of mathematical analysis and into the realm of practical measurements. The Agilent 54600 scope with Measurement/Storage Module uses

a particular algorithm, called the Fast Fourier Transform (FFT), for computing the DFT. The FFT and DFT produce the same result and the feature is commonly referred to as simply the FFT.

# II. FFT Implementation

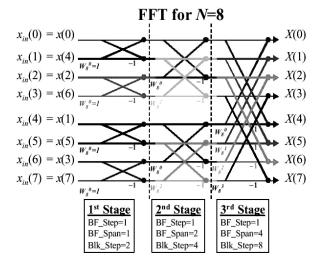

Fig 3.3 FFT implementation

we can see the different stages. In stage 1, there are 4 blocks, with one butterfly-per-block. In stage 2, there are two blocks with 2 butterflies each; and finally, in stage 3, there is only one block, combining all 8 coefficients with 4 butterflies.

Decimation in time FFT:

Number of stages =  $log_2N$

Number of blocks/stage =  $N/2^{stage}$

Number of butterflies/block =  $2^{\text{stage-1}}$

Table 1 FFT Implementation

| Start Index             | 0     | 0     | 0     |

|-------------------------|-------|-------|-------|

| Input Index             | 1     | 2     | 4     |

| Twiddle<br>Factor Index | N/2=4 | 4/2=2 | 2/2=1 |

| Indices used            | W0    | W0    | W0    |

|                         |       | W2    | W1    |

|                         |       |       | W2    |

|                         |       |       | W3    |

|                         |       |       |       |

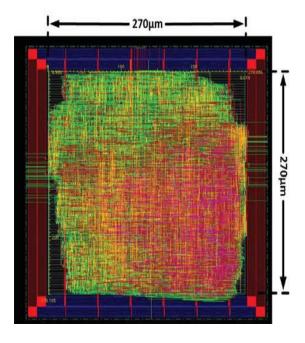

III. Layout Design

Fig 3.4 Layout of the FFT engine (0.73 mm2 in 45-nm CMOS technology)

# IV. SIMULATION AND OUTPUT

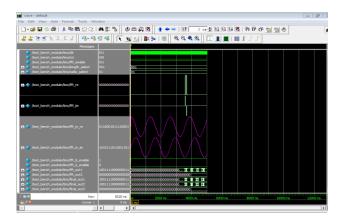

# A) Output for fixed point FFT verification

Fig.4.1 Fixed point FFT verification with sine & cosine waves

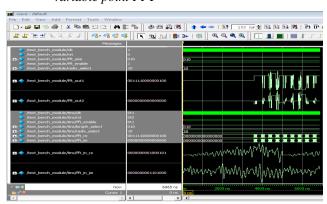

# B) Output for sample selection

Fig.4.2 sample selection with fixed rate for single and multi tone signals

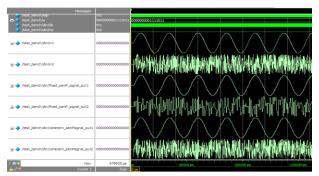

# C) FFT spectrum for multi tone signals with variable point FFT

Fig 4.3 spectrum for multi tone signals with variable point fft

# D) Spectrum for multi tone signals using coherent sampled FFT

Fig.4.4 FFT spectrum for multi tone signals with fixed point coherent sampled FFT

## E) Area optimization

TABLE II

Comparison for fixed point and variable point FFT

| FFT type           | Area<br>complexity | Speed    | Power       |

|--------------------|--------------------|----------|-------------|

| Fixed point<br>FFT | 256                | 4.079 Ps | 46.37<br>mw |

| Variable point FFT | 1025               | 5.952 Ps | 68.09<br>mw |

#### VI. CONCLUSION

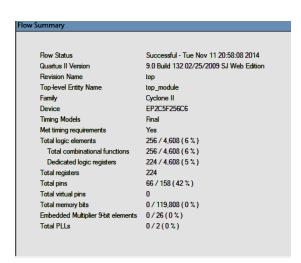

Here, we proved that coherent sampling based FFT will give better hardware complexity & power optimization with considerable delay enhancement. An accurate FFT-based analysis approach was introduced for FFT core with single and multi tone point spectral characterizations. The proposed approach was derived from the coherent sampling method. The method avoids the use of a large number of FFT points to minimize the required resources for area- and power-efficient built-in testing applications. Modelsim based pre simulation results of an FFT implementation showed the feasibility of the approach. For a QUARTUS II based hardware synthesis report of 16-point FFT computation, the implemented FFT engine consumes an estimated power of 46.37mW and occupies an area of 256 LE's which almost 4 times less as compared to variable point FFT.

#### REFERENCES

- [1] A. P. Jose, K. A. Jenkins, and S. K. Reynolds, "On-chip spectrum analyzer for analog built-in self test," in *Proc. IEEE VLSI Test Symp.*, May 2005.

- [2] Y.-W. Lin, H.-Y.Liu and C.-Y.Lee, "A 1-GS/s FFT/IFFT processor for UWB applications," *IEEE J. Solid-State Circuits*, vol. 40, no. 8, Aug. 2005.

- [3] D. Belega, M. Ciugudean, and D. Stoiciu, "Choice of the cosine-class Windows for ADC dynamic testing by spectral analysis," *Measurement*, vol. 40, no. 4, May 2007.

- [4] Y. Chen, Y.-C.Tsao, Y.-W.Lin, C.-H.Lin and C.-Y.Lee, "An indexed- scaling pipelined FFT processor for OFDM-based WPAN applications," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 2, Feb. 2008.

- [5] H.-M. Chang, M.-S.Lin and K.-T. Cheng, "Digitally-assisted analog/RFtesting for mixed-signal SoCs," *in Proc. 17th IEEE Asian Test Symp.*, Nov. 2008.

- [6] M. Onabajo, J. Silva-Martinez, F. Fernandez, and E. Sánchez-Sinencio, "An on-chip loopback block for RF transceiver built-in test," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 6, Jun. 2009.

- [7] H. Shin, J. Park, and J. A. Abraham, "Spectral prediction for specification-based loopback test of embedded mixed-signal circuits," *J. Electron. Test.*, vol. 26, no. 1, Jan. 2010